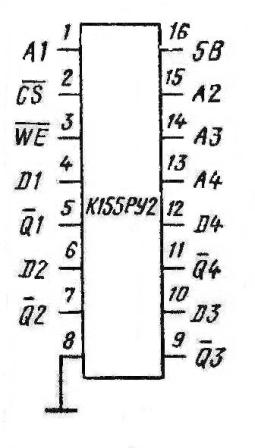

К155РУ2 (7489)

Микросхема К155РУ2 (7489) — высокоскоростное ОЗУ с емкостью 64 бит. Данные в ОЗУ можно записывать и считывать. При считывании информации из ОЗУ она не разрушается. Ячейки в памяти организованы в матрицу RAM, имеющую 16 рядов и 4 колонки, что соответствует логической организации 16 слов по 4 бита каждое. Матрица снабжена адресным дешифратором DC, который принимает четырехразрядный код адреса А1 — А4 и выбирает с помощью одного из своих 16 выходов нужное четырехразрядное слово. Четыре буферных входа данных D1 — D4 снабжены входом разрешения записи WE. Каждый выход данных Q1 — Q4 имеет открытый коллектор, что упрощает соединение нескольких ОЗУ К155РУ2 (7489) в более сложные маттицы. Данные на выходах инвертированы относительно тех, которые Описаны в памяти.

Если выбран режим записи, то входы и выходы имеют комплементарные коды. Для считывания данных из ОЗУ после фиксации адресных данных на вход WE подается напряжение высокого уровня, на вход доступа к нужной микросхеме памяти (условное название: вход выбора кристалла) CS — низкого. Для записи сигналов К155РУ2 (7489) требуется установить напряжение низкого уровня на входах управления E и CS. Адресный код в это время также должен быть зафиксирован.

Следует учесть, что в режиме считывания выбранные ячейки памяти доступны для приема данных, поэтому логические сигналы на шинах требуется зафиксировать перед переключением уровней управления от низкого к высокому на входах CS или WE.

Микросхема К155РУ2 (7489) потребляет ток 100 мА. Стекающей в открытый коллектор выходной ток более 24 мА. Выбрать режимы работы памяти К155РУ2 (7489) можно из таблицы.

Зарубежным аналогом микросхемы К155РУ2 являеются микросхема 7489.

| Режимработы | Вход | Выход Qn | ||

|---|---|---|---|---|

| CS | WE | Dn | ||

| Запись | Н | Н | Н | В |

| Н | Н | В | Н | |

| Считывание | Н | В | х | Dn |

| Запрет записи | В | Н | Н | В |

| В | Н | В | Н | |

| Отключение выходов | В | В | х | В |