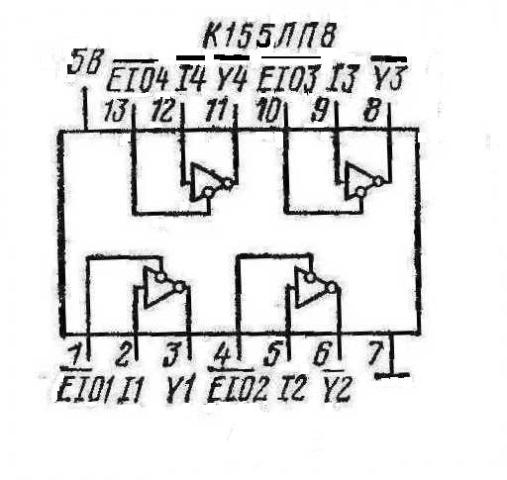

К155ЛП8, КМ155ЛП8 (74125)

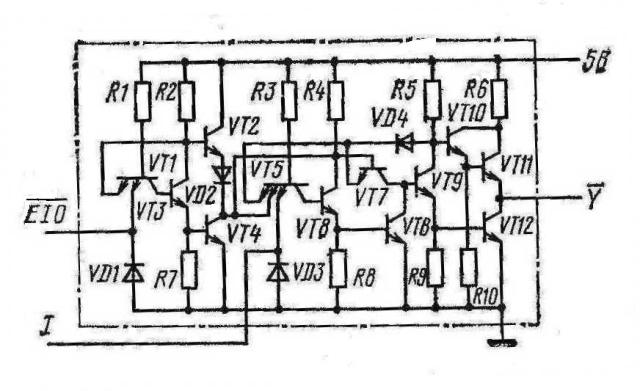

Микросхема К155ЛП8 (74125) представляет собой 4 буферных элемента с общей шиной и тремя состояниями. На рисунке дана схема одного канала микросхемы К155ЛП8 (74125). Здесь напряжением низкого уровня, поданным на общий для сигнального входа и выхода вывод разрешения EI0, действие входа I инвертора запрещается, а выход Y переводится в состояние Z. Выходной стекающий ток низкого уровня Ioвых может достигать 70 мА.

Зарубежным аналогом микросхем К155ЛП8, КМ155ЛП8 являются микросхемы 74125, SN74125N, SN74125J.

| Номинальное напряжение питания | 5В ± 5% |

| Выходное напряжение низкого уровня | ≤ 0,4 В |

| Выходное напряжение высокого уровня | ≥ 2,4 В |

| Напряжение на антизвонном диоде | ≥ -1,5 В |

| Входной ток низкого уровня | ≤ -1,6 мА |

| Входной ток высокого уровня | ≤ 0,04 мА |

| Входной пробивной ток | ≤ 1 мА |

| Ток короткого замыкания | -28...-70 мА |

| Ток потребления | ≤ 54 мА |

| Выходной ток при запрещении (Iзвых) - ток, протекающий в выходной цепи схемы в третьем состоянии (отключение от нагрузки) | ≤ ± 40 мА |

| Потребляемая статическая мощность на один логический элемент | ≤ 70,9 мВт |

| Время задержки распространения при включении | ≤ 18 нс |

| Время задержки распространения при выключении | ≤ 13 нс |

| Время задержки распространения сигнала запрещения в состоянии логического 0 | ≤ 13 нс |

| Время задержки распространения сигнала запрещения в состоянии лог.1 (t1,3 - время, за которое ИС переходит из состояние 1 в третье состояние при подаче на управляющий вход сигнала запрешения | ≤ 9 нс |

| Время задержки распространения сигнала разрешения в состоянии логического 0 | ≤ 25 нс |

| Время задержки распространения сигнала разрешения в состоянии логической 1 | ≤ 17 нс |

| Вход | Выход | |

|---|---|---|

| E10 | I | Y |

| Н | Н | Н |

| Н | В | В |

| В | х | Z |